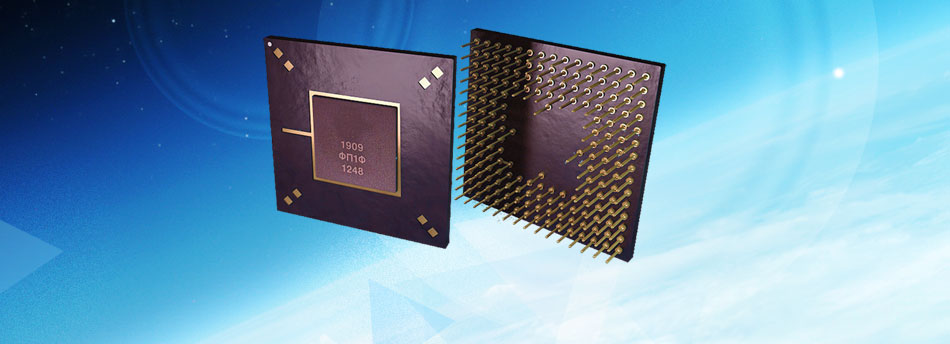

Digital signal Processor 1879 ВМ 6Y

- Purpose: - processing of broadband radar signals, including various types of digital filtering, Fourier, Hadamard transforms and others; - image processing (including various types of filtering and MPEG encoding and decoding); - navigation; - high-performance signal switching; - CDMA and TDMA base stations of cellular communication.

| Parameter | Value |

|---|---|

| Type of shell | HSBGA-544L |

| Supply voltage | cores – 1,0 V; peripherals CMOS – 3,3 V; peripherals SSTL – 1,8 V |

| Leakage current | low level at the input of the CMOS buffer: 10 μA (UIL = 0 V, UCC1 = 3.6 V); high level at the input of the CMOS buffer: 10 μA (UIL = 3.6 V, UCC1 = 3.6 V); low level at the input of the SSTL buffer: 10 μA (UCC2 = 1.95V); high level input SSTL buffer: 10 μA (UCC2 = 1.95V) |

| Working temperature, °C | -45 +85 |

| Technology | CMOS 90 nm |

| Type of acceptance | 5 |

| Frequency | 500 MHz |

High performance digital signal processor.

The processor architecture is based on the use of the new generation VLIW / SIMD processor core NMC4.

The processor contains two processor cores NMPU0 and NMPU1, each of which includes a RISC processor and a vector coprocessor.

- The first 64-bit coprocessor is designed to perform vector-matrix operations on integer data of variable length from 1 to 64 bits.

- The second 64-bit coprocessor is for floating-point vector operations.

Legal information

Please note that this site is for informational purposes only and under no circumstances is not a public offer determined by the provisions of the Part 2 Article 437 of the Civil code of the Russian Federation.

Information on this site may be changed or supplemented.